# Fabrication of Vertical Light Emitting Diode Based on Thermal Deformation of Nanoporous GaN and Removable Mechanical Supporter

Jin-Ho Kang,<sup>†</sup> Mohamed Ebaid,<sup>†</sup> June Key Lee,<sup>‡</sup> Tak Jeong,<sup>§</sup> and Sang-Wan Ryu<sup>\*,†</sup>

<sup>†</sup>Department of Physics, Chonnam National University, Gwangju 500-757, Korea

<sup>‡</sup>Department of Materials Science and Engineering, Chonnam National University, Gwangju 500-757, Korea

<sup>§</sup>Korea Photonics Technology Institute, Gwangju 500-779, Korea

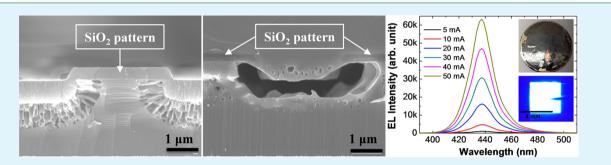

**ABSTRACT:** A GaN vertical light emitting diode (LED) based on the novel lift-off method was demonstrated by high temperature regrowth over nanoporous (NP) GaN template formed by electrochemical (EC) etching. A two-step EC etching process was employed on a SiO<sub>2</sub> patterned GaN surface to fabricate a nanoporous template with a controlled porosity profile, which enabled better structural stability than a single NP GaN. During the regrowth of LED structures, the high porosity GaN layer produced large coalesced voids due to the thermal deformation of nanopores. LED layers were then separated from the sapphire substrate and transferred to a Mo substrate by the removal of the SiO<sub>2</sub> mechanical supporters that held the LED structure to suppress cracks and damage during the process. The vertical LEDs fabricated using this technique showed improved optical power emission as well as low series resistance.

KEYWORDS: vertical light emitting diode, lift-off, GaN, nanoporous, electrochemical etching, regrowth

# INTRODUCTION

GaN based III–V compound semiconductors have attracted considerable interest in optical and electrical devices such as light emitting diodes (LEDs) and high electron mobility transistors.<sup>1–3</sup> However, due to the lack of native substrate for GaN homoepitaxial growth, GaN and its alloys are most commonly grown heteroepitaxially on a sapphire substrate. GaN grown on a sapphire substrate was reported to contain high density threading dislocations<sup>4,5</sup> generated at GaN/ sapphire interface because of the dissimilar lattice constants and thermal expansion coefficients between them.<sup>6</sup> In addition, the performance of LED was limited by poor thermal and electrical conductivities of the sapphire substrate.<sup>7</sup> Therefore, using conductive substrates may be beneficial for realizing an efficient current injection and thermal management properties.

The substrate separation process was previously performed by the laser lift-off (LLO) method.<sup>8</sup> In this method, a high power KrF excimer laser was employed to decompose the interfacial GaN into gaseous nitrogen and liquid gallium, resulting in the separation of the sapphire substrate. However, LED devices suffered from dislocations and lattice deformation in the active areas generated by high temperature and shock wave during LLO.<sup>9</sup> Concerning these LLO-related issues, a new technique called chemical lift-off (CLO) was developed to detach the GaN epilayer from the sapphire substrate.<sup>10–12</sup> For example, *n*-GaN under device layers was selectively removed laterally by electrochemical (EC) etching,<sup>10</sup> which led to the separation of the device structure from the substrate. Despite the several advantages of the CLO process such as low cost and no damage during the process, it is hardly commercially applicable because of the low etch rate and damage to bonding metals. Therefore, the GaN based-LED industry has demanded a new technique for obtaining free-standing GaN epilayers with simple process steps and high yield.

The shape deformation of nanopores caused by the surface migration of atoms at high temperature was studied to demonstrate the coalesced voids beneath the epitaxial structure.<sup>13,14</sup> Recently, based on the thermal deformation, the mechanical lift-off of GaN epitaxial layers was also developed. This lift-off process involved three main steps: (1) the formation of nanopores by EC etching, (2) the transformation of nanopores into nanovoids to reduce the structural

Received:March 13, 2014Accepted:April 30, 2014Published:April 30, 2014

## **ACS Applied Materials & Interfaces**

stability of regrown LED epilayers by high temperature regrowth, and (3) bonding to a transfer substrate and mechanical lift-off of regrown LED layers. However, the formation of an empty space beneath the device structure significantly degraded the structural stability, which caused severe problems such as cracking and defect formation in the LED active structure.

In this work, we fabricated a vertical LED using a new lift-off method based on the shape deformation of nanopores at high temperature and selective removal of  $SiO_2$  mechanical supporters after bonding. In this design,  $SiO_2$  supporters hold the LED structure to suppress crack and defect formation during the process and release the LEDs after bonding by their selective removal in HF. Vertical LED chips were fabricated, and their optical and electrical properties were analyzed in detail.

## EXPERIMENTAL WORK

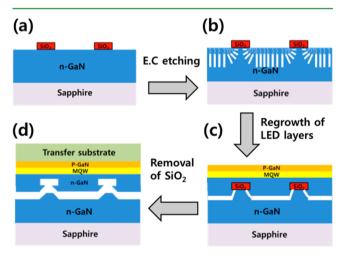

The GaN layers used in this work were grown on a c-plane sapphire substrate by metal organic chemical vapor deposition (MOCVD). The structure consisted of a low temperature GaN buffer, a 1- $\mu$ m-thick unintentionally doped GaN layer, and a 2- $\mu$ m-thick n-GaN layer. A 200 nm-thick SiO<sub>2</sub> layer was deposited on *n*-GaN by plasma-enhanced chemical vapor deposition. SiO<sub>2</sub> stripe patterns of 3  $\mu$ m/3  $\mu$ m (mask/window) width were then fabricated by conventional photolithography and wet etching as schematically shown in Figure 1a. EC etching was

**Figure 1.** Conceptual process flow of epitaxial lift-off starting from (a) patterned  $SiO_2$  on *n*-GaN, (b) EC etching, (c) the regrowth of LED layers, and (d) wafer bonding and the release of LED structures by removing  $SiO_2$ .

carried out in 0.3 M oxalic acid at room temperature.<sup>10</sup> The sample was immersed in oxalic acid and biased electrically such that the

sample became the anode, whereas a Pt wire immersed in the electrolyte served as a cathode. The applied voltage was varied (10 V - 3 min, 16 V - 4 min) to produce different porosity steps during the EC etching (Figure 1b).

After careful cleaning, the NP GaN sample was reloaded into the MOCVD reactor for growth of the LED structure, consisting of *n*-GaN (3  $\mu$ m), 5 pairs of InGaN/GaN multiquantum wells (MQWs), and p-type GaN (1  $\mu$ m). During the high temperature regrowth of *n*-GaN, the high porosity layer was transformed into a large void and the low porosity layer was sealed through the surface diffusion of atoms. The LED structure was then bonded to a metal (Mo) transfer substrate after the deposition of metal films (Ni/Au/Sn/Au) by Au/Sn eutectic bonding. The lift-off of the LED structure from the sapphire substrate was performed by removing the SiO<sub>2</sub> mechanical supporter in HF at 90 °C as shown in Figure 1d. Lifted-off LEDs on the metal substrate were diced in two different sizes ( $250 \times 250 \ \mu$ m<sup>2</sup> and  $1 \times 1 \ mm^2$ ) using a diamond saw for preparing the LED chips. Device performance of LEDs was characterized by electroluminescence (EL), voltage–current (*V*–*I*), and optical power–current (*L*–*I*) measurements.

In order to compare the device performance of a vertical LED (V-LED) with a conventional LED, lateral LEDs (L-LEDs) were fabricated with the same growth condition of *n*-GaN, MQW, and p-GaN without the lift-off. For the L-LED process, a Ni/Au (3 nm/5 nm) current spreading layer was deposited on top,<sup>15</sup> which was the only difference in the layer structure from V-LED. N-type contact was made on *n*-GaN after the reactive ion etching of the *n*-metal pad. The L-LED was then diced into chips of the same sizes with V-LED.

## RESULTS AND DISCUSSION

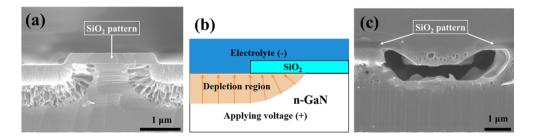

Figure 2a shows a typical SEM cross sectional image of NP GaN after EC etching. The low and high porosity layers in GaN were formed between  $SiO_2$  patterns using two-step etching (10 V, 16 V) and the porosity of GaN was changed with the applied voltage. The procedure of forming NP GaN by EC etching has been previously reported.<sup>10,16</sup> The voltage applied to GaN anode produced holes at the surface by tunneling of valence electrons, resulting in oxidation etching of GaN. The etching morphology was known to depend on anodic voltage and doping concentration. Consequently, we could control the etching morphology of GaN by varying voltage for the grown sample. The deposited SiO<sub>2</sub> patterns at the surface of GaN deformed the propagation behavior of the nanoporous etching around the SiO<sub>2</sub> from a vertical to a horizontal direction. Figure 2b shows a schematic view of the effect of the patterned  $SiO_2$ mask on the carrier depletion under reverse bias, where it modified the electric field near its edge. After the EC etching process, the high porosity layer became mechanically weak, which could cause spontaneous lift-off of the top layer, but areas below the SiO<sub>2</sub> mechanical supporters were protected as shown in Figure 2a. The low porosity layer was connected to the substrate through the SiO<sub>2</sub> pattern, which offered high structural stability after EC etching as well as after regrowth.

Figure 2. Cross-sectional SEM images of (a) nanopores after EC etching and (c) coalesced voids after regrowth. (b) Schematic drawing of the depletion region and electric field at the interface between the electrolyte and *n*-GaN.

The structural stability could be controlled by increasing the thickness of the  $SiO_2$  supporter and contact area between the low porosity layer and  $SiO_2$ .

Shape deformation of nanopores was induced by surface atomic diffusion driven by the minimization of the surface energy at elevated temperature. As discussed in the theory of Rayleigh instabilities,<sup>17<sup>-</sup></sup> atoms diffuse down a gradient in the surface chemical potential from the larger curvature region toward the lower curvature region of the cylindrical surface. In this study, the shape deformation of nanopores was accomplished through the high temperature GaN regrowth on the NP GaN template. N-GaN was regrown on NP GaN at 1090 °C for 105 min (3  $\mu$ m GaN growth) and layers for the LED structure were then sequentially grown. During the regrowth, cylindrical pores were transformed into spherical voids, keeping the volume of the cavity unchanged.<sup>16,18-20</sup> Therefore, after the shape deformation, the spherical void was connected to the neighboring voids, and it eventually formed an empty space in GaN as shown in Figure 2c. The high porosity layer was transformed into a large void between the SiO<sub>2</sub> patterns, while low porosity GaN was nearly sealed through surface diffusion.

The high porosity layer formed by two-step EC etching led to the formation of an empty space without the appearance of pillars, which were difficult in the conventional single step EC etching process. In some papers, a certain number of nanopillars were necessary for preventing spontaneous lift-off of the regrown layer, but too many pillars were disadvantageous for clear lift-off after wafer bonding.<sup>16,21</sup> However, in this study, the regrown LED structure was supported by patterned SiO<sub>2</sub> stripes that could eliminate the need for the nano pillars. This allowed more flexibility over the regrowth condition and a higher yield of the LED process. In addition, SiO<sub>2</sub> patterns may possess two additional benefits: (1) enhanced crystal quality of regrown LED layers due to threading dislocation bent around the SiO<sub>2</sub> pattern<sup>22,23</sup> and (2) reduced strain of the regrown GaN layer with air voids.<sup>16</sup>

In order to demonstrate the wafer scale lift-off of the LED structures from the sapphire substrate, the LED wafer was bonded to a foreign metal substrate by Au/Sn eutetic bonding and was then immersed in HF at 90 °C for 3 h. During HF treatment, the LED structure formed on the 2-in. wafer was spontaneously lifted off from the sapphire by the removal of SiO<sub>2</sub> mechanical supporters. It is worth mentioning that after the lift-off of the LED layers, there was a remaining GaN layer on the sapphire substrate with the thickness of ~1.5  $\mu$ m, hereafter called the base GaN substrate.

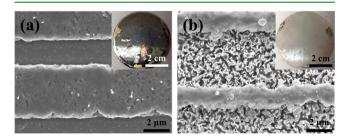

Figure 3 shows SEM images displaying the microscopic surface roughness for the bottom face of lifted-off GaN and the

Figure 3. Plane-view SEM images of (a) the bottom face of lifted-off GaN and (b) the top surface of base GaN substrate. The insets show corresponding optical images of the 2-in. wafer.

top surface of base GaN substrate. The insets show the wafer scale lift-off of the LED layers and the remaining base GaN substrate. Both the lifted-off GaN and base GaN displayed a nanoscale roughened surface between the SiO<sub>2</sub> stripes, which was formed by the thermal deformation of nanopores during the regrowth. The rough surface of the lifted-off GaN combined with the trace of SiO<sub>2</sub> patterns will be advantageous to increase light extraction efficiency by hybrid micro/nano patterns.<sup>24</sup> In addition, the base GaN substrates can be recycled for repetitive growth and subsequent lift-off of LED layers by this route, offering the great reduction of substrate cost even for expensive and high quality GaN substrates.

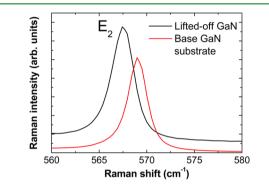

The strain states of both the lifted-off GaN layer and the base GaN substrate were investigated by Raman spectroscopy. Figure 4 shows that the Raman peak shifts of the  $E_2$  phonon

Figure 4. Raman spectra of  $\mathrm{E}_2$  mode of lifted-off GaN and base GaN substrate.

mode for the lifted-off GaN layer and the base GaN substrate were 569.0 and 567.4 cm<sup>-1</sup>, respectively. The Raman peak shift of the lifted-off GaN was similar to that of a fully strain relaxed GaN layer, which was attributed to the regrowth on the coalesced voids and the release from the substrate. On the other hand, the base GaN substrate exhibited smaller amounts of stress (0.36 GPa) than that of the as-grown GaN (0.83 GPa)<sup>16</sup> on the sapphire substrate. This reduced strain would have originated from the nanoscale roughened surfaces formed by the thermal deformation of the nanopores and the coalescence of the voids, as depicted in Figure 3b. Furthermore, the low strain and rough surface of the base GaN may enable the growth of high quality GaN,<sup>25</sup> which will allow better performance LEDs by base GaN recycling.

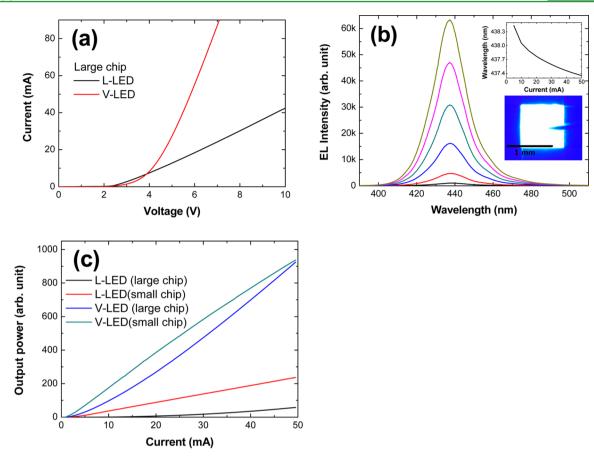

Figure 5a shows the measured V–I characteristics of large chip (1 × 1 mm<sup>2</sup> area) V-LED and L-LED. V-LED had ~5 times lower series resistance than the L-LED due to its vertical current flow geometry and improved p-Ohmic contact resistance. The low series resistance helped to suppress the current crowding effect and to reduce heat generation in the LED chip. Figure 5b shows the room temperature EL spectra and optical image of large chip V-LED. The peak emission wavelength of V-LED was around 438 nm and slightly blueshifted with the injection current that was caused by the band filling effect in the InGaN MQW.<sup>26</sup> The emission pattern represented a uniform light intensity distribution over the entire chip area. This implied that negligible current crowding occurred in V-LED, which was consistent with the V–I results.

Figure 5c compares the optical power of V-LED and L-LED with different chip sizes. First, the output power was much higher for V-LED than L-LED when the chip size was fixed. For example, the large chip V-LED showed  $\sim 16$  times higher

Figure 5. (a) I-V characteristics of large chip L-LED and V-LED and (b) room temperature electroluminescence spectra of large chip V-LED at 5, 10, 20, 30, 40, and 50 mA. The insets are (top) the plot of emission peak wavelength vs injection current and (bottom) optical image of light emission pattern of V-LED. (c) L-I characteristics of V-LED and L-LED for large and small chips.

optical emission power than L-LED at 50 mA. This indicated that V-LED had high external quantum efficiency originating from the high light extraction efficiency, fast heat dissipation, suppressed current crowding, and better epitaxial growth quality, etc.

It is interesting to monitor the chip-size dependent device efficiency for different LED structures. For V-LED, the chip area did not make a considerable difference in L-I performance; however, for L-LED, the large chip showed severe optical power degradation compared to the small chip  $(250 \times 250)$  $\mu$ m<sup>2</sup>). This behavior could be explained by the limiting factor of the device performance for each structure. Because of the flat surfaces, L-LED had narrow escape cones for top and sidewall light extractions. With larger chip dimension, the performance of L-LED was limited by light extraction from chip sidewalls and poor light extraction was obtained. The contribution of sidewall light extraction diminished with the chip size because the light power contained in sidewall escape cone decrease.<sup>27</sup> However, V-LED showed excellent light extraction from top surface due to the roughened chip surface and the contribution of chip sidewalls might not be significant. The light extraction efficiency of V-LED did not degrade with the chip size.

In addition, the optical power reduction of the large chip was decreasing with the operation current for V-LED. This was observed in V-LED because it has high light extraction efficiency, even for the large chip. Therefore, the suppression of efficiency droop by the low carrier density was more dominant with the increase of the operation current. This behavior demonstrated that V-LED fabricated using this technique is promising for high efficiency and high power LED production for solid state lightings or other advanced applications.

## CONCLUSION

In conclusion, we fabricated GaN-based V-LED chips on a metal substrate using the lift-off method based on thermal deformation of nanopores during the regrowth of LED structures with the aid of SiO<sub>2</sub> mechanical supporters. SiO<sub>2</sub> patterns protected the low porosity GaN layer from lift-off during EC etching, while the high porosity GaN layer was transformed into coalesced voids at high temperature. After bonding to a metal substrate, LED full structures formed on a 2-in. sapphire wafer were separated by removing the SiO<sub>2</sub> supporters via etching in HF acid. Because of the high extraction efficiency of V-LEDs caused by hybrid micro/nano patterns, V-LEDs showed huge improvement of light output power over L-LEDs. We believe that this lift-off process could produce economical V-LED chips with greatly improved device performances.

#### AUTHOR INFORMATION

#### **Corresponding Author**

\*Tel.: +82-62-530-3476. Fax: +82-62-530-3369. E-mail: sangwan@chonnam.ac.kr.

#### Notes

The authors declare no competing financial interest.

## ACKNOWLEDGMENTS

This work was supported by the National Research Foundation of Korea Grant funded by the Korean Government (NRF-2013R1A1A2059179, NRF-2011-0017190).

#### REFERENCES

(1) del Alamo, J. A.; Joh, J. GaN HEMT Reliability. *Microelectron. Reliab.* **2009**, *49*, 1200–1206.

(2) Xia, L.; Hanson, A.; Boles, T.; Jin, D. On Reverse Gate Leakage Current of GaN High Electron Mobility Transistors on Silicon Substrate. *Appl. Phys. Lett.* **2013**, *102*, 113510.

(3) Okumura, H. Present Status and Future Prospect of Widegap Semiconductor High-power Devices. *Jpn. J. Appl. Phys.* 2006, 45, 7565–7586.

(4) Hsueh, K.-P.; Hsin, Y.-M.; Sheu, J.-K.; Lai, W.-C.; Tun, C.-J.; Hsu, C.-H; Lin, B.-H. Effects of Leakage Current and Schottky-like Ohmic Contact on the Characterization of  $Al_{0.17}GaN_{0.83}N/GaN$ HBTs. *Solid-State Electron.* **2007**, *51*, 1073–1078.

(5) Narayanan, V.; Lorenz, K.; Kim, W.; Mahajan, S. Origins of Threading Dislocations in GaN Epitaxial Layers Grown on Sapphire by Metalorganic Chemical Vapor Deposition. *Appl. Phys. Lett.* **2001**, 78, 1544–1546.

(6) Cho, S. I.; Chang, K.; Kwon, M. S. Strain Analysis of a GaN Epilayer Grown on a c-Plane Sapphire Substrate with Different Growth Times. J. Mater. Sci. 2007, 42, 3569–3572.

(7) Huang, S.; Wu, H.; Fan, B.; Zhang, B.; Wang, G. A Chip-Level Electrothermal-Coupled Design Model for High-Power Light-Emitting Diodes. *J. Appl. Phys.* **2010**, *107*, 054509.

(8) Wong, W. S.; Sands, T.; Cheung, N. W. Damage-Free Separation of GaN Thin Films from Sapphire Substrates. *Appl. Phys. Lett.* **1998**, 72, 599–601.

(9) Cheng, J.-H.; Wu, Y. S.; Peng, W. C.; Ouyang, H. Effects of Laser Sources on Damage Mechanisms and Reverse-bias Leakages of Laser Lift-off GaN Based LEDs. J. Electrochem. Soc. **2009**, 156, H640–H643.

(10) Park, J.; Song, K. M.; Jeon, S.-R.; Baek, J. H.; Ryu, S.-W. Doping Selective Lateral Electrochemical Etching of GaN for Chemical Liftoff. *Appl. Phys. Lett.* **2009**, *94*, 221907.

(11) Rogers, D. J.; Teherani, F. H.; Ougazzaden, A.; Gautier, S.; Divay, L.; Lusson, A.; Durand, O.; Wyczisk, F.; Garry, G.; Monteiro, T.; Correira, M. R.; Peres, M.; Neves, A.; McGrouther, D.; Chapman, J. N.; Razeghi, M. Use of ZnO Thin Films as Sacrificial Templates for Metal Organic Vapor Phase Epitaxy and Chemical Lift-off of GaN. *Appl. Phys. Lett.* 2007, *91*, 071120.

(12) Lin, C.-F.; Dai, J.-J.; Wang, G.-M.; Lin, M.-S. Chemical Lift-off Process for Blue Lift-emitting Diodes. *Appl. Phys. Express* **2010**, *3*, 092101.

(13) Yerino, C. D.; Zhang, Y.; Leung, B.; Lee, M. L.; Hsu, T.-C.; Wang, C.-K.; Peng, W.-C.; Han, J. Shape Transformation of Nanoporous GaN by Annealing: From Buried Cavities to Nanomembranes. *Appl. Phys. Lett.* **2011**, *98*, 251910.

(14) Mizushima, I.; Sato, T.; Taniguchi, S.; Tsunashima, Y. Empty-Space-in-Silicon Technique for Fabricating a Silicon-on-nothing Structure. *Appl. Phys. Lett.* **2000**, *77*, 3290–3292.

(15) Chen, Z. Z.; Qin, Z. X.; Tong, Y. Z.; Hu, X. D.; Yu, T. J.; Yang, Z. J.; Ding, X. M.; Li, Z. H.; Zhang, G. Y. Thermal Annealing Effects on Ni/Au Contacts to p-type GaN in Different Ambient. *Mater. Sci. Eng.*, B **2003**, *100*, 199–203.

(16) Kang, J.-H.; Lee, J. K.; Ryu, S.-W. Lift-off of Epitaxial GaN by Regrowth over Nanoporous GaN. J. Cryst. Growth. 2012, 361, 103–107.

(17) Rayleigh, L. The Instability of Jets. Proc. London Math. Soc. 1878, S1-10, 4.

(18) Mullins, W. W. Theory of Thermal Grooving. J. Appl. Phys. 1957, 28, 333-339.

(19) Nichols, F. A.; Mullins, W. W. Morphological Changes of a Surface of Revolution due to Capillarity-Induced Surface Diffusion. *J. Appl. Phys. Lett.* **1965**, *36*, 1826–1835.

(20) Srolovitz, D. J.; Safran, S. A. Capillary Instabilities in Thin Films. I. Energetics. J. Appl. Phys. **1986**, 60, 247–254.

(21) Zhang, Y.; Leung, B.; Han, J. A Liftoff Process of GaN Layers and Devices through Nanoporous Transformation. *Appl. Phys. Lett.* **2012**, *100*, 181908.

(22) Hiramatsu, K.; Nishiyama, K.; Onishi, M.; Mizutani, H.; Narukawa, M.; Motogaito, A.; Miyake, H.; Iyechika, Y.; Maeda, T. Fabrication and Characterization of Low Defect Density GaN using Facet-Controlled Epitaxial Lateral Overgrowth (FACELO). *J. Cryst. Growth.* **2000**, *221*, 316–326.

(23) Sakai, A.; Sunakawa, H.; Kimura, A.; Usui, A. Self-Organized Propagation of Dislocations in GaN Films during Epitaxial Lateral Overgrowth. *Appl. Phys. Lett.* **2000**, *76*, 442–444.

(24) Cho, J. Y.; Byeon, K.-J.; Park, H.; Kim, J.; Kim, H.-S.; Lee, H. Improvement of Photon Extraction Efficiency of GaN-based LED using Micro- and Nano-complex Polymer Structures. *Nanoscale Res. Lett.* **2011**, *6*, 578.

(25) Soh, C. B.; Hartono, H.; Chow, S. Y.; Chua, S. J.; Fitzgerald, E. A. Dislocation Annihilation in Regrown GaN on Nanoporous GaN Template with Optimization of Buffer Layer Growth. *Appl. Phys. Lett.* **2007**, *90*, 053112.

(26) Wang, L.; Lu, C.; Lu, J.; Liu, L.; Liu, N.; Chen, Y.; Zhang, Y.; Gu, E.; Hu, X. Influence of Carrier Screening and Band Filling Effects on Efficiency Droop of InGaN Light Emitting Diodes. *Opt. Express* **2011**, *19*, 1482.

(27) Chu, C.-F.; Cheng, C.-C.; Liu, W.-H.; Chu, J.-Y.; Fan, F.-H.; Cheng, H.-C.; Doan, T.; Tran, C. A. High Brightness GaN Vertical Light-Emitting Diodes on Metal Alloy for General Application. *Proc. IEEE* **2010**, *98*, 1197.